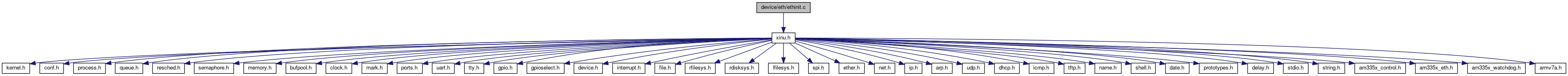

#include <xinu.h>

Go to the source code of this file.

Functions | |

| int32 | eth_phy_read (volatile struct eth_a_mdio *mdio, byte regadr, byte phyadr, uint32 *value) |

| int32 | eth_phy_reset (volatile struct eth_a_mdio *mdio, byte phyadr) |

| int32 | eth_phy_write (volatile struct eth_a_mdio *mdio, byte regadr, byte phyadr, uint32 value) |

| int32 | ethinit (struct dentry *devptr) |

Variables | |

| struct eth_a_csreg | eth_a_regs |

| struct ethcblk | ethertab [1] |

Function Documentation

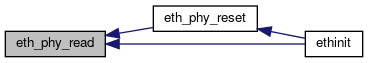

◆ eth_phy_read()

| int32 eth_phy_read | ( | volatile struct eth_a_mdio * | mdio, |

| byte | regadr, | ||

| byte | phyadr, | ||

| uint32 * | value | ||

| ) |

Definition at line 13 of file ethinit.c.

References ETH_AM335X_MDIOUA_ACK, ETH_AM335X_MDIOUA_DM, ETH_AM335X_MDIOUA_GO, OK, SYSERR, and eth_a_mdio::useraccess0.

Referenced by eth_phy_reset(), and ethinit().

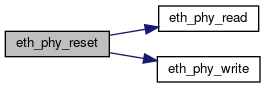

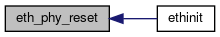

◆ eth_phy_reset()

| int32 eth_phy_reset | ( | volatile struct eth_a_mdio * | mdio, |

| byte | phyadr | ||

| ) |

Definition at line 107 of file ethinit.c.

References DELAY, ETH_AM335X_INIT_DELAY, ETH_PHY_CTLREG, ETH_PHY_CTLREG_RESET, eth_phy_read(), ETH_PHY_STATREG, ETH_PHY_STATREG_LINK, eth_phy_write(), OK, and SYSERR.

Referenced by ethinit().

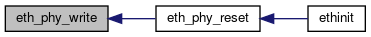

◆ eth_phy_write()

| int32 eth_phy_write | ( | volatile struct eth_a_mdio * | mdio, |

| byte | regadr, | ||

| byte | phyadr, | ||

| uint32 | value | ||

| ) |

Definition at line 64 of file ethinit.c.

References ETH_AM335X_MDIOUA_GO, ETH_AM335X_MDIOUA_WR, OK, SYSERR, and eth_a_mdio::useraccess0.

Referenced by eth_phy_reset().

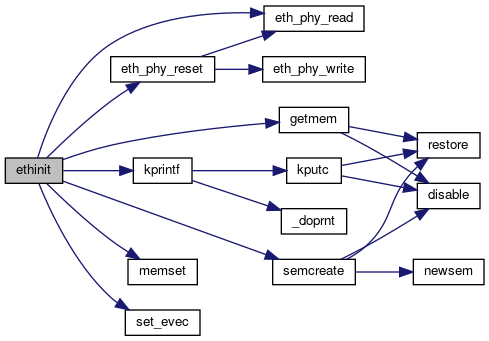

◆ ethinit()

Definition at line 173 of file ethinit.c.

References eth_a_csreg::ale, eth_a_rx_desc::buffer, eth_a_tx_desc::buffer, eth_a_rx_desc::buflen, eth_a_tx_desc::buflen, eth_a_rx_desc::bufoff, eth_a_tx_desc::bufoff, eth_a_wr::c0_rx_en, eth_a_wr::c0_tx_en, eth_a_csreg::cpdma, ethcblk::csr, eth_a_ale::ctrl, eth_a_mdio::ctrl, ethcblk::devAddress, dentry::dvintr, dentry::dvminor, eth_a_regs, ETH_AM335X_ALE_ADDR, ETH_AM335X_ALECTL_BY, ETH_AM335X_ALECTL_EN, ETH_AM335X_ALEPCTL_FWD, ETH_AM335X_CPDMA_ADDR, ETH_AM335X_MDIO_ADDR, ETH_AM335X_MDIOCTL_EN, ETH_AM335X_RDS_OWN, ETH_AM335X_RX_RING_SIZE, ETH_AM335X_RXINT, ETH_AM335X_SL1_ADDR, ETH_AM335X_SLCTL_EN, ETH_AM335X_SLCTL_FD, ETH_AM335X_SS_ADDR, ETH_AM335X_STATERAM_ADDR, ETH_AM335X_TDS_DIR, ETH_AM335X_TDS_EOP, ETH_AM335X_TDS_P1, ETH_AM335X_TDS_SOP, ETH_AM335X_TX_RING_SIZE, ETH_AM335X_TXINT, ETH_AM335X_WR_ADDR, ETH_BUF_SIZE, ETH_PHY_1000M, ETH_PHY_100M, ETH_PHY_10M, ETH_PHY_CTLREG, ETH_PHY_CTLREG_FD, ETH_PHY_CTLREG_SM, eth_phy_read(), eth_phy_reset(), ethertab, getmem(), ethcblk::isem, kprintf(), eth_a_sl::macctrl, eth_a_csreg::mdio, memset(), netpacket::net_ethdst, eth_a_rx_desc::next, eth_a_tx_desc::next, NULL, NULLCH, OK, ethcblk::osem, eth_a_ale::portctl, eth_a_cpdma::reset, eth_a_sl::reset, eth_a_ss::reset, eth_a_wr::reset, eth_a_cpdma::rx_ctrl, eth_a_stateram::rx_hdp, eth_a_cpdma::rx_intmask_set, ethcblk::rxBufs, ethcblk::rxHead, ethcblk::rxRing, ethcblk::rxRingSize, ethcblk::rxTail, semcreate(), set_evec(), eth_a_csreg::sl, eth_a_csreg::ss, eth_a_rx_desc::stat, eth_a_tx_desc::stat, eth_a_csreg::stateram, SYSERR, eth_a_cpdma::tx_ctrl, eth_a_stateram::tx_hdp, eth_a_cpdma::tx_intmask_set, ethcblk::txBufs, ethcblk::txHead, ethcblk::txRing, ethcblk::txRingSize, ethcblk::txTail, and eth_a_csreg::wr.

Variable Documentation

◆ eth_a_regs

| struct eth_a_csreg eth_a_regs |

◆ ethertab

| struct ethcblk ethertab[1] |

Definition at line 7 of file ethinit.c.

Referenced by ethcontrol(), ethhandler(), ethinit(), ethread(), and ethwrite().

1.8.13

1.8.13